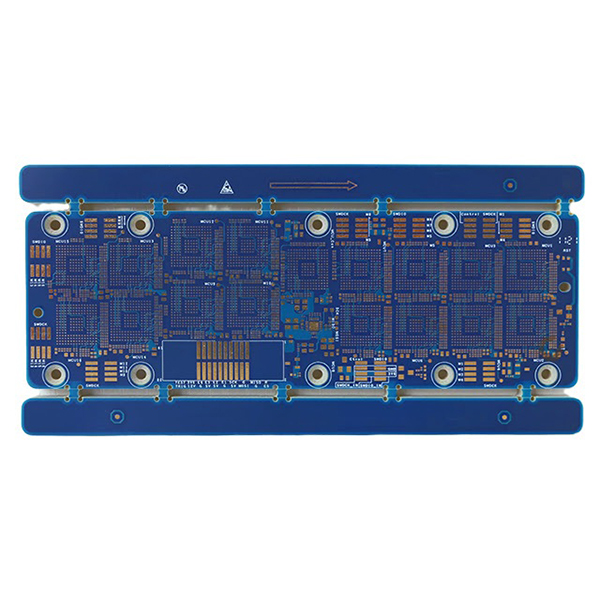

Виробництво 14-шарової 3-ступеневої напівпровідникової тестової плати

Виробництво 14-шарових 3-ступеневих напівпровідникових тестових плат PCB є одним з основних процесів у галузі тестування напівпровідникових мікросхем, що забезпечує високу продуктивність апаратного забезпечення для тестування функцій мікросхем та перевірки надійності.

Опис

14-шарова, 3-ступенева плата для тестування напівпровідників Виробництво друкованих плат

Виробництво 14-шарових, 3-ступеневих друкованих плат для тестування напівпровідників, що відрізняються високою щільністю, високою точністю та високою надійністю, широко використовується в різних сучасних приладах для тестування напівпровідників і служить ключовою основою для забезпечення якості та продуктивності мікросхем.

Основні характеристики 14-шарового, 3-етапного виробництва друкованих плат для тестування напівпровідників

- Багатошарове з’єднання високої щільності:14-шарова структура в поєднанні з 3-етапною технологією HDI підтримує складні схеми розміщення та ізоляцію багатосигнальних сигналів, відповідаючи вимогам до передачі сигналів з високою щільністю та швидкістю.

- Точний виробничий процес:Використовується високоякісний матеріал Shengyi S1000-2M з позолоченою поверхнею, мінімальним діаметром отвору 0,5 мм і мінімальним проміжком/відстанню 4/4 міл, що підходить для потреб тестування з дрібним кроком і високою точністю.

- Висока надійність і цілісність сигналу:Передова технологія прихованих/сліпих переходів та міжшарових з’єднань значно покращує цілісність сигналу та протидію перешкодам, забезпечуючи точність тестових даних.

- Відмінні матеріали та майстерність виготовлення:Висока стійкість до високих температур і корозії, підходить для довготривалих і складних умов тестування.

- Гнучкий дизайн і можливість налаштування:Підтримка різних тестових інтерфейсів та індивідуальних конструкцій, що полегшує інтеграцію в різні тестові системи.

Вступ до 14-шарової, 3-ступеневої напівпровідникової тестової плати

- 14 шарів:Відноситься до 14 провідних шарів всередині друкованої плати, що забезпечує складні схеми з’єднань і ізоляцію сигналів за допомогою багатошарового укладання, підходить для вимог до високої щільності та швидкості сигналів, а також сприяє цілісності сигналів та електромагнітній сумісності.

- 3 етапи:Зазвичай відноситься до «етапів» у технології HDI (High Density Interconnect) — три процеси лазерного свердління та три процеси ламінування, що підтримують більш тонкі структури заглиблених/сліпих переходів для більш гнучких з’єднань та вищої щільності, що підходить для високошвидкісних/високочастотних застосувань.

- Плата для тестування напівпровідників:Спеціально використовується для таких функцій, як тестування функцій мікросхем та тестування на старіння, що вимагає високої надійності, високої точності та відмінної здатності до передачі сигналу.

Основні застосування

- Системи тестування напівпровідників, такі як пристрої для тестування мікросхем, автоматичне тестове обладнання ATE, пробні карти та навантажувальні плати.

- Високозатребувані сценарії тестування, такі як тестування функцій ІС, тестування на старіння та аналіз відмов.

- Підходить для упаковки та тестування напівпровідників, а також для досліджень і розробок, що вимагають високої частоти, швидкості, точності та надійності.

English

English  Français

Français  Tiếng Việt

Tiếng Việt  Italiano

Italiano  Nederlands

Nederlands  Türkçe

Türkçe  Svenska

Svenska  Polski

Polski  Română

Română  Latviešu

Latviešu  한국어

한국어  Русский

Русский  Español

Español  Deutsch

Deutsch  Українська

Українська  Português

Português  العربية

العربية  Indonesian

Indonesian  Čeština

Čeština  Suomi

Suomi  Eesti

Eesti  Български

Български  Dansk

Dansk  Lietuvių

Lietuvių  Bokmål

Bokmål  Slovenčina

Slovenčina  Slovenščina

Slovenščina  Ελληνικά

Ελληνικά  Magyar

Magyar  עברית

עברית